Kelemahan utama dari file sirkuit kombinasional adalah, ia tidak menggunakan memori apa pun untuk menyimpan keadaan sekarang dan sebelumnya. Oleh karena itu keadaan input sebelumnya tidak berpengaruh pada keadaan rangkaian saat ini. Sedangkan rangkaian sekuensial memiliki memori sehingga keluaran dapat bervariasi berdasarkan masukan. Jenis sirkuit ini menggunakan input, output, clock, dan elemen memori sebelumnya. Di sini elemen memori bisa berupa latch atau flip-flop. Rangkaian Sekuensial dirancang dengan berbagai metode seperti dengan menggunakan ROM dan membalik, PLA, CPLD (Perangkat Logika yang Dapat Diprogram Kompleks) , FPGA (Field Programmable Gate Array) . Pada artikel ini, kita hanya akan membahas tentang cara mendesain rangkaian sekuensial menggunakan PLA.

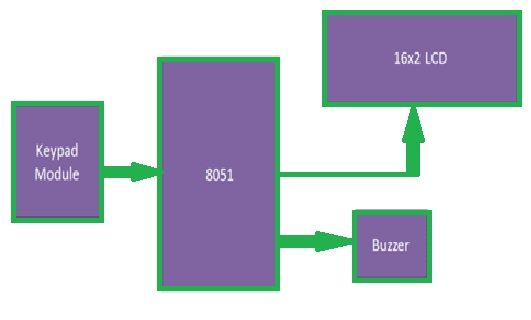

Diagram blok rangkaian sekuensial seperti yang ditunjukkan di bawah ini:

Diagram Blok Rangkaian Sekuensial

Merancang Rangkaian Sekuensial Menggunakan PLA

Sirkuit berurutan dapat direalisasikan menggunakan PLA (Programmable Logic Arrays) dan sandal jepit. Dalam desain ini, penugasan negara bagian mungkin penting karena penggunaan penugasan negara bagian yang baik dapat mengurangi jumlah persyaratan produk yang dibutuhkan dan, karenanya mengurangi ukuran PLA yang diperlukan. Istilah produk yang didefinisikan sebagai konjungsi literal, di mana setiap literal dapat berupa variabel atau negasinya.

Untuk mari kita pertimbangkan desain konverter kode. Tabel status yang ditunjukkan di bawah dalam tabel dapat direalisasikan dengan menggunakan satu PLA dan tiga sandal jepit seperti gambar di bawah ini. Konfigurasi rangkaian ini sangat mirip dengan desain berbasis ROM flip-flop, kecuali bahwa ROM diganti dengan PLA dengan ukuran yang sesuai. Tugas negara mengarah ke tabel kebenaran yang diberikan di bawah ini. Tabel ini dapat disimpan dalam PLA dengan empat masukan, 13 istilah produk, dan empat keluaran, tetapi ini akan menawarkan sedikit pengurangan ukuran dibandingkan dengan ROM 16 kata.

| X Q1 Q2 Q3 | Dengan D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabel: Tabel Kebenaran

MENYAJIKAN NEGARA

| NEGARA BERIKUTNYA X = 0 1 | MENYAJIKAN OUTPUT (Z) |

| UNTUK | B C | 1 0 |

B C | D E Dan E | 1 0 0 1 |

D AKU S | H H H M | 0 1 1 0 |

H. M | A A UNTUK - | 0 1 1 - |

Tabel: Tabel Status

Perancangan Rangkaian Sekuensial Menggunakan PLA

Persamaan Input Output Diturunkan oleh Karnaugh Map

Di sini, karena ada tujuh status, diperlukan tiga sandal jepit D. Dengan demikian, diperlukan rangkaian PLA dengan 4 masukan dan 4 keluaran. Jika penetapan status konverter kode diperhatikan, persamaan keluaran yang dihasilkan dan persamaan masukan D flip-flop yang diturunkan dari Karnaugh dapat dituliskan persamaan berikut

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X Q1 Q2 Q3 | Dengan D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 sebelas

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Tabel PLA yang sesuai dengan persamaan ini diberikan pada tabel di atas. Tabel ini dapat direalisasikan dengan menggunakan PLA dengan empat masukan, tujuh istilah produk, dan empat keluaran. Untuk memverifikasi pengoperasian desain di atas pada awalnya, asumsikan bahwa X = 0 dan Q1Q2Q3 = 000. Ini memilih baris - - 0- dan 0 - - -0 dalam tabel, jadi Z = 0 dan D1D2D3 = 100. Setelah tepi jam aktif, Q1Q2Q3 = 100. Jika masukan berikutnya adalah X = 1, maka baris - - 0 - dan - 1- - dipilih, sehingga Z = 0 dan D1D2D3 = 110. Setelah tepi jam aktif, Q1Q2Q3 = 110.

Programmable Logic Array (PLA)

Programmable Logic Array adalah perangkat logis yang dapat diprogram. Biasanya digunakan untuk mengimplementasikan rangkaian logika kombinasional. PLA memiliki seperangkat bidang AND yang dapat diprogram (larik AND), yang ditautkan ke sekumpulan bidang OR yang dapat diprogram (larik OR), yang kemudian dapat dilengkapi untuk sementara untuk menghasilkan keluaran. Tata letak ini memungkinkan sejumlah besar fungsi logika untuk disintesis di jumlah produk (SOP) bentuk kanonik. Diagram blok sederhana PLA diberikan di bawah ini.

Diagram Blok dari PLA

Perbedaan utama antara PLA dan PAL (logika array yang dapat diprogram) adalah,

PLA: Keduanya DAN pesawat dan ATAU pesawat dapat diprogram.

PAL: Hanya bidang AND yang dapat diprogram, sedangkan bidang OR ditetapkan.

Untuk pemahaman yang lebih baik tentang PLA, di sini kami mempertimbangkan contoh di bawah ini.

Mari kita coba untuk mengimplementasikan fungsi ini f1 dan f2 diberikan sebagai

Input x1, x2, x3 dan masing-masing sinyal komplemen diberikan ke bidang AND yang dapat diprogram, di sana kita akan mendapatkan output bidang AND sebagai minterm yang disebut P1, P2, P3. Kemudian sinyal ini diberikan ke bidang OR yang dapat diprogram untuk menghasilkan fungsi keluaran yang diperlukan f1 dan f2 (jumlah produk). Gambar di bawah ini menjelaskan implementasi level gerbang PLA untuk fungsionalitas yang diberikan.

Implementasi PLA

Ini semua tentang Mendesain Rangkaian Sekuensial Menggunakan PLA. Kami menganggap bahwa informasi yang diberikan dalam artikel ini bermanfaat bagi Anda untuk lebih memahami konsep ini. Selanjutnya, pertanyaan apa pun tentang artikel ini atau bantuan apa pun di melaksanakan proyek listrik dan elektronik , Anda dapat mendekati kami dengan berkomentar di bagian komentar di bawah. Ini pertanyaan untukmu, Apa yang dimaksud dengan rangkaian sekuensial?